[2021-04-20] DiAG: A Dataflow-Inspired Architecture for General-Purpose Processors

Published:

In my point of view, it is basically a spatial dataflow architecture with more general compatiblity.

Difference from dataflow architecture

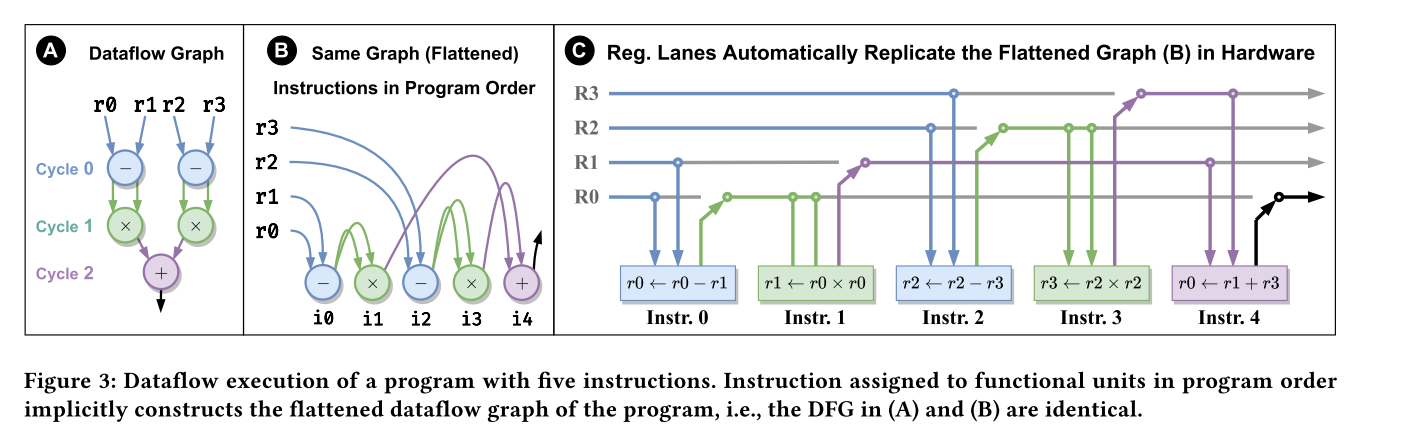

- instructions are assigned in program order, but execute out-of-order

- use register lanes instead of register file to contruct a dataflow graph and serve as a reorder buffer

- PEs are chained rather than a 2D array

Pros and Cons

Dynamic datapaths constructed by DiAG are reusable, thus loop iterations can execute at an efficiency close to accelerators

- On the other hand, applications that are memory-centric or contain significant control divergence perform poorly since most cycles are wasted on stalls

- area overhead

My questions

Why CGRA could not be a main processor, but only be a co-processors?