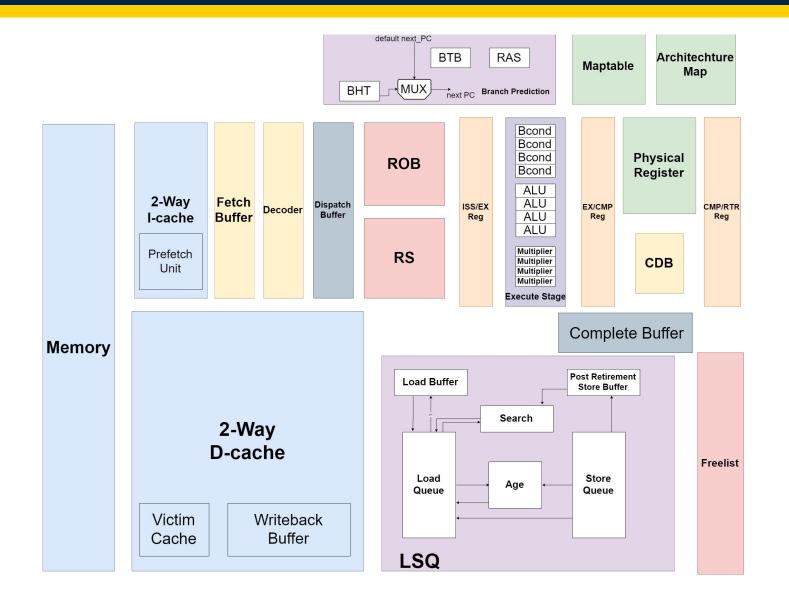

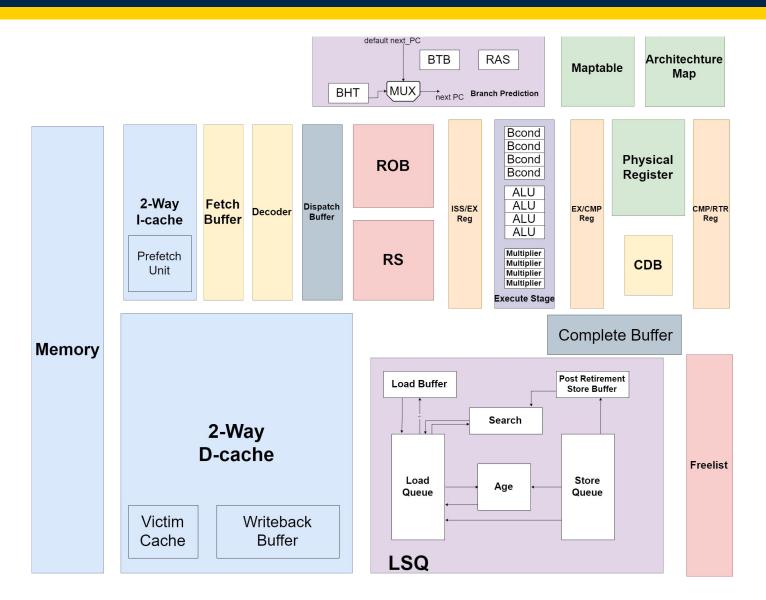

EECS 470 Computer Architecture Project Presentation

## Risc V 4-way Superscalar R10K OoO Processor

## **Group 8 OoO** Xiuneng Lu, Siyu Niu, Yunjie Pan, Runyu Zheng

Dec. 11th, 2019

## Features

| Features                                      | Included | Comments                                 |

|-----------------------------------------------|----------|------------------------------------------|

| RISC V R10k OoO Processor                     | Yes      |                                          |

| Graphical debugging Tool                      | Yes      | print contents of each buffer each cycle |

| Automated regression testing infrastructure   | Yes      | Run all tests and compare rst w/ P3      |

| Superscalar                                   | Yes      | Superwidth $= 4$                         |

| Store-to-load forwarding in LSQ               | Yes      | We have, but only for SW                 |

| Loads issue out-of-order past pending stores  |          |                                          |

| (non-speculative)                             | Yes      | As described                             |

| Post-retirement store buffer                  | Yes      | 16 entries                               |

| Multiple outstanding load misses              | Yes      | Hide miss lantancy                       |

| Next-line or stride prefetching for           |          |                                          |

| instructions and/or data                      | Yes      | Prefetch next 16 instructions            |

| Write-back data cache                         | Yes      | write back & write allocate              |

| Associativity > 1                             | Yes      | 2-Way                                    |

| Victim cache                                  | Yes      | 64 bit                                   |

| Return address stack                          | Yes      | 16 entries                               |

|                                               |          |                                          |

| Loads speculatively issue past pending stores | No       | Implemented. but still buggy             |

|                                               |          | Implemented, worked, but inefficient     |

| Load dependence predictor                     | No       | and influence critical path too much     |

3

| cycle: 22<br>Step: 1 MemIn MemOut Ktag tag d ktag tag tag tag tag tag tag tag tag tag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROD       MOD       M | e       inva       e       inva       e       inva       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e       e                                                                                                                                                                                                                                                                                             |

| Cleacher         v         PC         inst inst v         PC         inst inst           0         +         0         addi         nop         0         inva           1         +         8         addi         inva         inva         inva           3         +         18         sw         addi         inva         inva           3         +         18         sw         addi         inva         inva           5         +         28         sw         addi         inva         inva           7         +         38         nop         sub         0         inva         inva           10         0         inva         inva         0         inva         inva         inva           11         0         inva         0         inva         inva         1         1         0         inva         0         1         0         2         0         inva         1         0         2         0         1         0         2         0         1         0         2         0         1         0         2         0         1         0         2            | LindQ         C         t         ddr +         ddr +< |

4

PC1 +

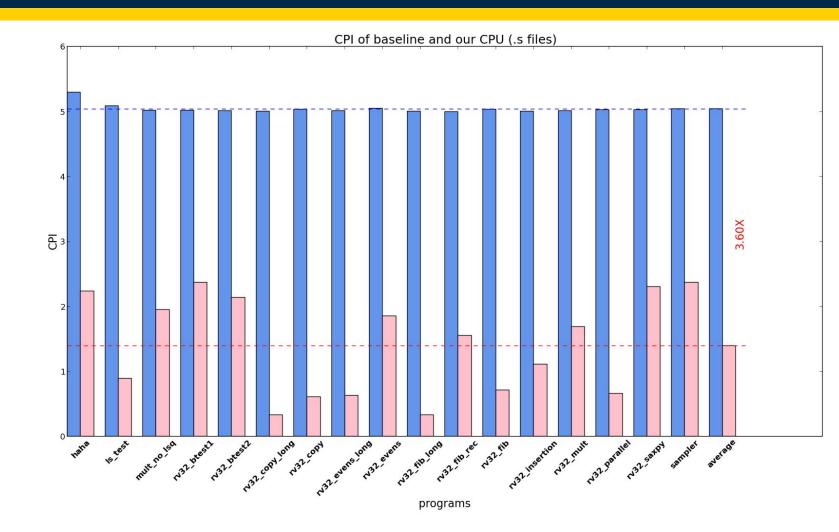

for public testcase(.s files)

baseline average CPI=5.04

our average CPI = 1.40

27.8% of baseline

clock cycle @Synthesis 17ns

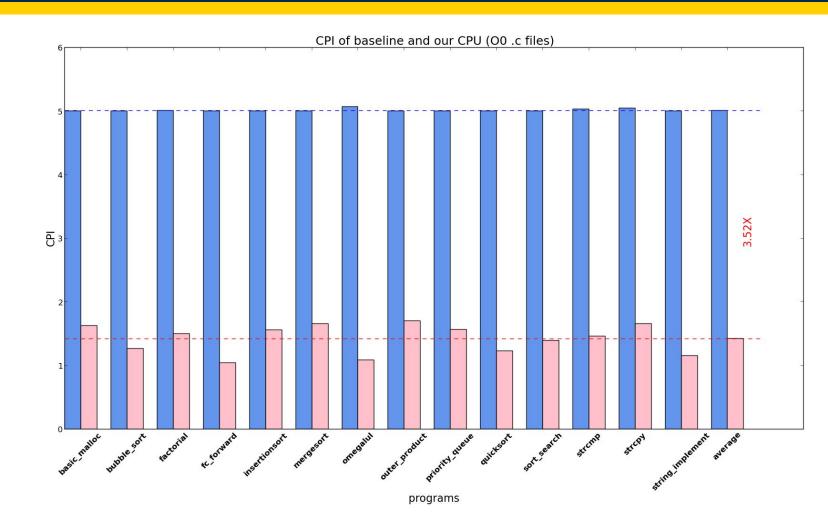

for public testcase(.c files) with O0 optimization

baseline average CPI=5.01

our average CPI = 1.42

28.4% of baseline

clock cycle @Synthesis 17ns

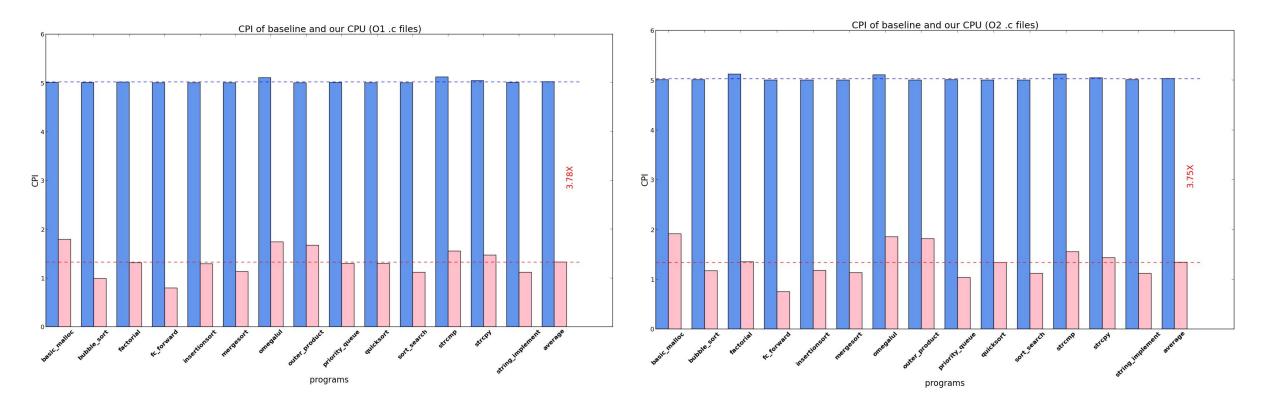

-O1 average CPI = 1.32

-O2 average CPI = 1.34

## **ECE** Starting it all over again...

- Leave more time for Optimization

- We spent too much time on implementing the feature

- Always thinking the hardware cost before implementing large structures

- Always assign a initial value for a variable

- simulate may assert xxx as 0 but synthesis may not

- Finish debugging speculative load and load dependence predictor